# UNIVERSITA' POLITECNICA DELLE MARCHE

# FACOLTA DI INGEGNERIA

Corso di Laurea in Ingegneria Elettronica

"Convertitori DC-AC multilivello per amplificatori in classe D con controllo sigma-delta"

Relatore: Chiar.mo Tesi di Laurea di:

Prof. Simone Orcioni Giacomo Di Filippo

A.A. 2018/2019

# **INDICE**

|    | INTROL | OUZIONE       |                                    | 1  |

|----|--------|---------------|------------------------------------|----|

| 1. | DESCRI | ZIONE DEI     | LL'AMPLIFICATORE                   | 2  |

|    | 1.1.   | Struttura de  | ell'amplificatore in classe D      | 2  |

| 2. | INVERT | TER MULTI     | LIVELLO                            | 6  |

|    | 2.1.   | Struttura rea | alizzativa                         | 6  |

|    | 2.2.   | Vantaggi de   | ell'architettura multilivello      | 8  |

|    | 2.3.   | Tipologie     |                                    | 9  |

|    |        | 2.3.1.        | Diode clamped inverter             | 10 |

|    |        | 2.3.2.        | Floating capacitor inverter        | 15 |

|    |        | 2.3.3.        | Cascaded cell inverter             | 20 |

|    |        | 2.3.4.        | Inverter T-Type                    | 23 |

| 3. | MODUL  | AZIONE SI     | GMA-DELTA                          | 26 |

|    | 3.1.   | Introduzion   | e al sigma-delta                   | 26 |

|    | 3.2.   | Modulazion    | ne sigma-delta del primo ordine    | 28 |

|    | 3.3.   | Modulazion    | ne sigma-delta di ordine superiore | 30 |

| 4. | ARCHI  | TETTURA D     | EL MODULATORE SIGMA-DELTA          | 33 |

|    | 4.1.   | Modello de    | l modulatore                       | 33 |

|    | 4.2.   | Simulazion    | i del modulatore                   | 37 |

|    |        | 4.2.1.        | Risultati simulazioni a 1 MHz      | 39 |

|    |        | 4.2.2.        | Risultati simulazioni a 2 MHz      | 42 |

| 5. | ARCHI  | TETTURA D     | ELL'AMPLIFICATORE                  | 44 |

|    | 5.1.   | Modello de    | ll'amplificatore                   | 44 |

|    | 5.2.   | Simulazion    | i dell'amplificatore               | 47 |

| 6. | CONCL  | USIONI        |                                    | 49 |

|    | APPEN  | DICE          |                                    | 51 |

|    | BIBLIO | GRAFIA        |                                    | 58 |

# **ELENCO DELLE FIGURE**

- Figura 1.1 Schema generale rappresentativo dell'amplificatore in classe D qui proposto.

- Figura 1.2 Circuito di un inverter DC-AC a ponte intero o "a ponte H" da [3].

- Figura 1.3 Modello Simulink dell'altoparlante.

- Figura 2.1 Schema generale di un convertitore da tensione continua ad alternata.

- Figura 2.2 Circuito di un inverter a mezzo ponte.

- Figura 2.3 Circuito del diode clamped inverter da [6].

- Figura 2.4 Circuito del floating capacitor inverter da [6].

- Figura 2.5 Circuito del cascaded cell inverter da [6].

- Figura 2.6 Circuito dell'inverter T-Type da [4].

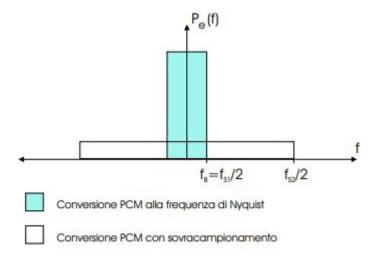

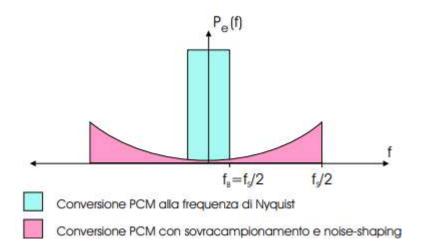

- Figura 3.1 Densità spettrale di potenza del rumore di quantizzazione per una conversione PCM alla frequenza di Nyquist e con sovra campionamento.

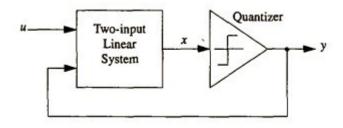

- Figura 3.2 Modello generale del sigma-delta da [15].

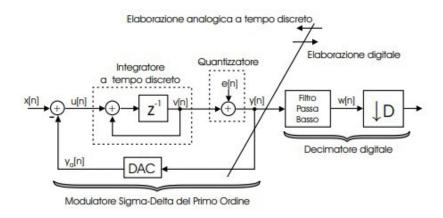

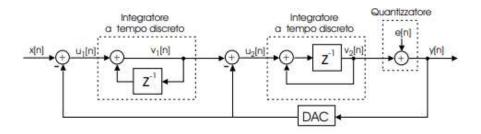

- Figura 3.3 Convertitore A/D con modulatore sigma-delta del primo ordine da [13].

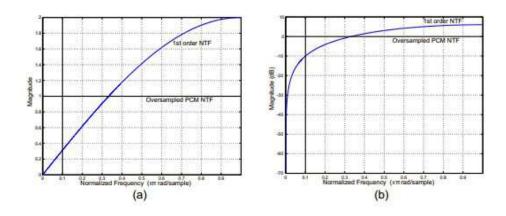

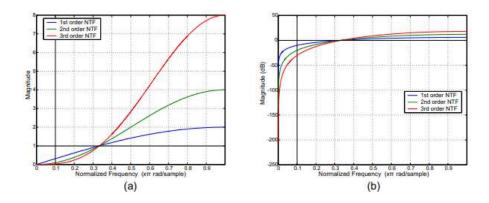

- Figura 3.4 NTF sigma-delta primo ordine: scala lineare (a), logaritmica in dB (b), da [13].

- Figura 3.5 Densità spettrale di potenza del rumore di quantizzazione per una conversione PCM alla frequenza di Nyquist e per una conversione PCM con sovracampionamento e noise-shaping.

- Figura 3.6 Modulatore sigma-delta del secondo ordine da [13].

- Figura 3.7 NTF per modulatori sigma-delta dal I al III ordine: spettri di ampiezza su scala lineare a confronto con la NTF del convertitore PCM a sovracampionamento con guadagno unitario; (a) scala lineare, (b) scala logaritmica in dB, da [13].

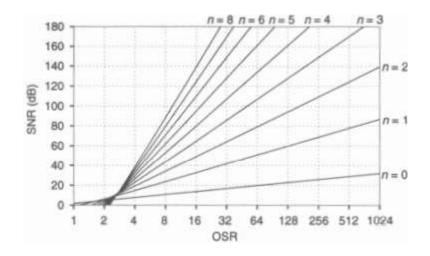

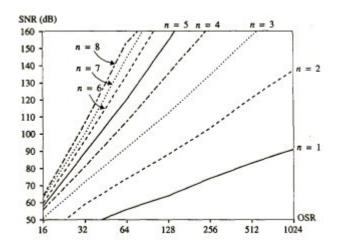

- Figura 3.8 SNR teorico per modulatore di ordine n da [14].

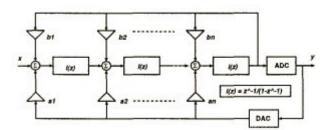

- Figura 4.1 Architettura sigma-delta a più livelli da [16].

- Figura 4.2 SNR massimo utilizzando posizionamento ottimo per gli zeri da [15].

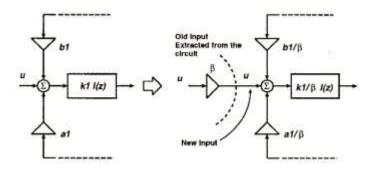

- Figura 4.3 Scalatura dell'ingresso u di un fattore β da [16].

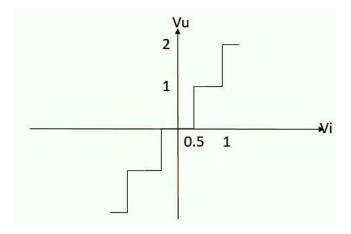

- Figura 4.4 Caratteristica del quantizzatore a cinque livelli.

- Figura 4.5 Quantizzatore utilizzato per il modello in Simulink.

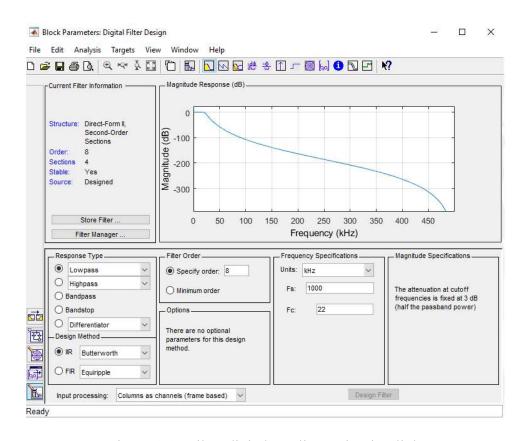

- Figura 4.6 Filtro digitale realizzato in Simulink.

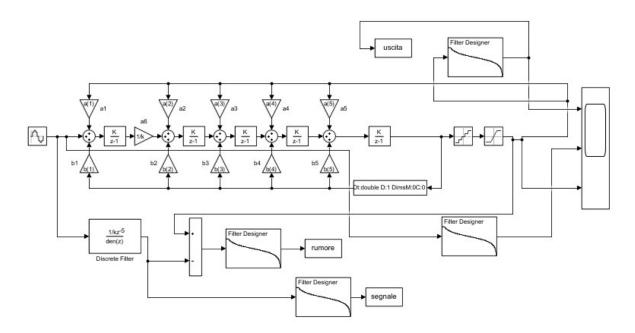

- Figura 4.7 Modello Simulink del modulatore sigma-delta.

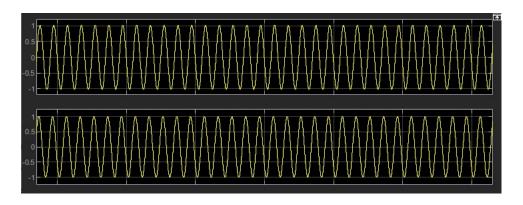

- Figura 4.8 Uscita (sopra) e ingresso (sotto) del sigma delta con quantizzatore a cinque livelli.

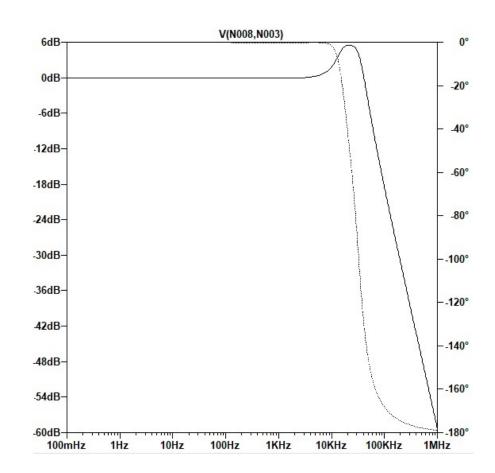

- Figura 4.9 Grafico della funzione di trasferimento del segnale o STF a 1 MHz.

- Figura 4.10 Grafico della funzione di trasferimento del rumore o NTF a 1 MHz.

- Figura 4.11 Grafico della funzione di trasferimento del segnale o STF a 2 MHz.

- Figura 4.12 Grafico della funzione di trasferimento del rumore o NTF a 2 MHz.

- Figura 5.1 Modello Simulink dell'inverter utilizzato.

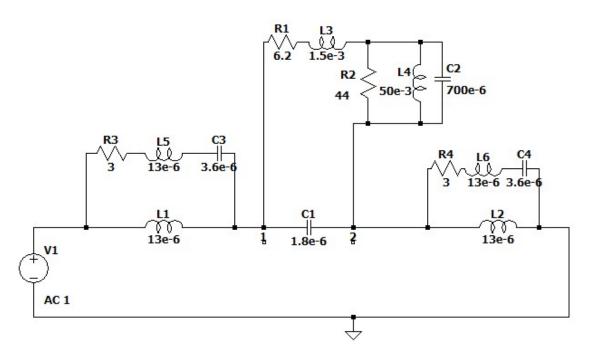

- Figura 5.2 Modello LTSpice del carico con filtro e altoparlante.

- Figura 5.3 Comportamento in frequenza della tensione sul carico: la linea continua è il modulo, la linea tratteggiata è la fase.

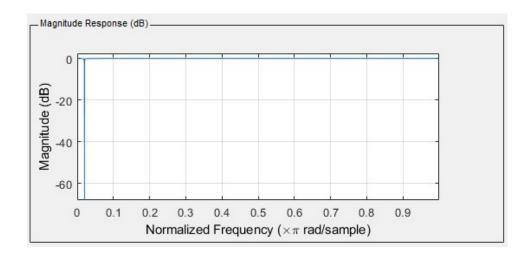

- Figura 5.4 Filtro utilizzato per il calcolo del rumore in uscita dall'amplificatore.

# ELENCO DELLE TABELLE

| Tabella 1.1 | Tabella rappresentativa degli stati assunti dal convertitore a ponte intero. |

|-------------|------------------------------------------------------------------------------|

| Tabella 2.1 | Tabella rappresentativa degli stati assunti dal convertitore a mezzo ponte.  |

| Tabella 2.2 | Tabella rappresentativa degli stati assunti dal diode clamped inverter.      |

| Tabella 2.3 | Tabella rappresentativa degli stati assunti dal floating capacitor inverter. |

| Tabella 2.4 | Tabella rappresentativa degli stati assunti dal cascaded cell inverter.      |

| Tabella 2.5 | Tabella rappresentativa degli stati assunti dall'inverter T-Type.            |

| Tabella 4.1 | Posizionamento ottimo degli zeri per aumentare l'SNR da [14].                |

| Tabella 4.2 | Tabella degli SNR ottenuti nelle simulazioni a 2 MHz.                        |

# **INTRODUZIONE**

In questa tesi si propone un modello di amplificatore audio in classe D, introdotto nel Capitolo 1, realizzato utilizzando una architettura multilivello a cinque livelli, in modo da migliorare il contenuto armonico dell'uscita grazie ad una maggiore risoluzione e utilizzando una modulazione sigma-delta invece della consueta PWM.

Nel Capitolo 2 vengono esposte le caratteristiche dell'inverter multilivello, del quale sono mostrate le architetture maggiormente impiegate per realizzarli, con particolare accezione per la topologia scelta per questa tesi, presentata nel paragrafo 2.3.4. Successivamente viene analizzata nel Capitolo 3 la modulazione sigma-delta, che è utilizzata in questo caso per il pilotaggio dell'inverter.

Viene quindi proposto nei Capitoli 4 e 5 il modello circuitale di questo amplificatore, realizzato utilizzando la piattaforma MATLAB/Simulink, in particolare il Simscape, e simulazioni di esso utilizzando una sinusoide come segnale di ingresso. Vengono mostrati anche i grafici delle tensioni di uscita che evidenziano un corretto funzionamento del circuito e nell'ultimo capitolo vengono esposte le conclusioni sul progetto.

# I DESCRIZIONE DELL'AMPLIFICATORE

In elettronica sono presenti diversi tipi di amplificatori audio [1] che differiscono tra di loro per alcuni fattori come il tempo di accensione degli interruttori e l'efficienza di lavoro dello stesso. Essi si distinguono in due grandi categorie: amplificatori analogici e digitali.

I più diffusi amplificatori analogici sono gli stadi di classe A, B, AB e sono anche definiti amplificatori lineari data la presenza di transistor in uscita che operano sempre linearmente. Questi stadi prendono in ingresso un segnale analogico per produrne in uscita uno ancora analogico e presentano come svantaggio il ridotto guadagno e le elevate perdite di potenza, dovute ai lunghi tempi di accensione dei transistor.

Al contrario gli amplificatori digitali, rappresentati in particolare dall'amplificatore in classe D, utilizzano dei transistor che lavorano come semplici interruttori in cui, dato un segnale digitale in ingresso, ne riproducono uno in uscita. Presentano quindi perdite molto minori e guadagni molto elevati, con un'efficienza che nella pratica si aggira intorno al 92-93%, e per questi motivi rappresenta la tipologia di amplificatore scelta.

## 1.1 STRUTTURA DELL'AMPLIFICATORE IN CLASSE D

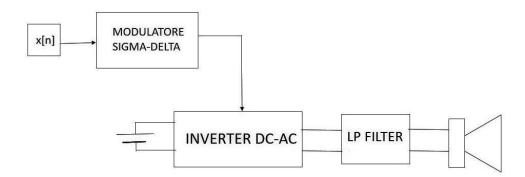

La struttura dell'amplificatore in classe D realizzato in questa tesi è mostrata in Figura 1.1 e può essere vista principalmente come una struttura a due stadi connessi tra di loro.

Figura 1.1 - Schema generale rappresentativo dell'amplificatore in classe D qui proposto.

Il primo stadio è composto da un modulatore sigma-delta, un componente che realizza una modulazione del segnale di ingresso a tempo discreto, dando ancora in uscita un segnale a tempo discreto. La caratteristica principale è data dal fatto che presenta alle basse frequenze il segnale stesso, con il rumore invece spostato alle alte frequenze, grazie al noise-shaping effettuato dal modulatore. Inoltre, si comporta anche come driver del circuito, permettendo il pilotaggio dei transistor dell'inverter.

Il secondo stadio dell'amplificatore è costituito da un inverter DC-AC, cioè un circuito che, data una tensione continua in ingresso, ne genera una alternata in uscita.

Solitamente viene utilizzata una architettura con quattro transistor posti a due a due in due rami, chiamata inverter a ponte intero [2], che permette di ottenere una uscita a tre livelli, in genere +Vdd, 0, -Vdd, dove Vdd rappresenta l'alimentazione in continua.

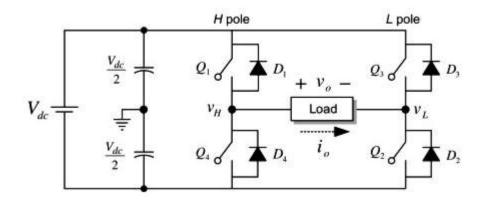

Un esempio di convertitore a ponte intero è mostrato in Figura 1.2:

Figura 1.2 - Circuito di un inverter DC-AC a ponte intero o "a ponte H".

Questo circuito è composto da quattro interruttori e una alimentazione in DC, in cui è presente anche un condensatore per effettuare il DC-link. Il funzionamento è piuttosto semplice e consiste nel pilotaggio dei transistor in modo da tenerne sempre due accesi contemporaneamente e si effettua un cambiamento dello stato in uscita effettuando la commutazione di due interruttori ogni volta. Gli stati ottenibili si trovano nella Tabella 1.1, dove si mostra solo lo stato di Q1 e Q3, considerando che gli interruttori nello stesso ramo, rispettivamente Q4 e Q2 hanno comportamento opposto, quindi se Q1 è acceso allora Q4 è spento.

| Stato | Q1  | Q3  | Vo   |  |

|-------|-----|-----|------|--|

| 00    | OFF | OFF | 0    |  |

| 01    | OFF | ON  | -Vdc |  |

| 10    | ON  | OFF | +Vdc |  |

| 11    | ON  | ON  | 0    |  |

Tabella 1.1 - Tabella rappresentativa degli stati assunti dal convertitore a ponte intero.

In questa configurazione sono presenti due rami in cui non sono mai accesi insieme i due transistor, cosa che creerebbe un cortocircuito e quindi un malfunzionamento che può portare anche alla rottura.

Nel primo stato 00 si hanno i due interruttori superiori spenti e i due inferiori accesi, ottenendo in uscita il livello di tensione nullo. Questo avviene poiché la corrente circola nella maglia di Q4 e D2, diodo di ricircolo di Q2, oppure nella maglia di Q2 e D4 e genera una differenza di tensione in uscita che vale zero. Questa ambiguità nel percorso della corrente dipende dalla direzione della stessa, rispettivamente in senso antiorario e senso orario.

Si ha la stessa situazione per lo stato 11, in cui sono accesi gli interruttori Q1 e Q3, ottenendo in uscita una tensione nulla. Il percorso della corrente in questo caso ha luogo nella maglia attraverso Q1 e D3 oppure Q3 e D1.

Nello stato 01 si genera il livello di tensione –Vdc tenendo accesi i transistor Q4 e Q3, facendo attenzione che, durante la commutazione, non si abbia un istante in cui siano accesi insieme i due interruttori nello stesso ramo per preservare il circuito.

Infine, nello stato 10 si accendono gli interruttori Q1 e Q2 e risulta in uscita una differenza di tensione pari a Vdc, dal momento che dal primo ramo esce una tensione di Vdc e dal secondo una nulla. Nella commutazione per ottenere questo valore bisogna sempre prendere le precauzioni appena dette per il corretto funzionamento del circuito.

Al contrario, per realizzare l'inverter usato in questa tesi è utilizzata un'architettura a cinque livelli, già presentata in [4] e mostrata nel paragrafo 2.3.4. Questa è ottenuta con un totale di cinque transistor, diversamente dal solito inverter a ponte intero a tre livelli.

Questa topologia è costituita da un ponte intero, quindi quattro transistor, più un quinto, che serve per generare ulteriori due livelli, in modo da ottenere un totale di cinque livelli e quindi una maggiore risoluzione e una minore distorsione armonica dell'uscita, quindi un contenuto armonico più pulito che permetta una riduzione nella complessità del filtro in uscita.

Infine, si trova il carico dell'inverter costituito da un filtro passa basso, realizzato con una rete LC a scala, e l'altoparlante. In particolare, questo dispositivo permette, dato un segnale elettrico in ingresso, di generare un segnale meccanico, cioè l'audio. Questo apparecchio può anche essere studiato in termini di comportamento elettrico ed approssimato utilizzando la rete RLC di Figura 1.3.

Figura 1.3 - Modello Simulink dell'altoparlante.

Una volta mostrata la struttura generale di questo amplificatore, si procede a descrivere ogni singola parte nel dettaglio, cominciando dall'inverter. Verranno mostrate le principali architetture usate e quella scelta in questa tesi, per poi analizzare il modulatore scelto, costituito dal modulatore sigma-delta.

### II INVERTER MULTILIVELLO

Gli inverter multilivello sono dei convertitori DC-AC che sviluppano una tensione di uscita su più livelli, portando con sé numerosi vantaggi rispetto ai classici inverter a mezzo ponte e a ponte intero. In particolare, si sta diffondendo molto l'uso nel mondo di queste nuove topologie e nella letteratura sono presenti molti tipi di inverter.

Ora andremo a presentare la struttura di questi circuiti per poi passare alla descrizione delle architetture maggiormente usate, tra cui, nel paragrafo 2.3.4, si trova quella scelta per la realizzazione dell'amplificatore presentato in questa tesi [4].

Infine, vengono spiegati i vantaggi e gli svantaggi degli inverter multilivello rispetto alla tecnologia precedentemente utilizzata.

#### 2.1 STRUTTURA REALIZZATIVA

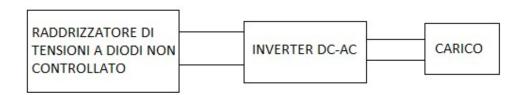

La struttura tipica dell'inverter è presente in Figura 2.1.

Figura 2.1 - Schema generale di un convertitore da tensione continua ad alternata.

L'inverter è un circuito che svolge il ruolo di convertitore DC-AC, cioè trasforma una tensione continua in ingresso in una tensione alternata di uscita, perciò presenta innanzitutto una alimentazione in continua, spesso ottenuta rettificando la tensione alternata di rete.

Questa va poi a fornire la tensione per l'architettura utilizzata, in genere costituita da diversi circuiti, denominati 'half-bridge', o mezzo ponte, opportunamente posizionati.

L' half-bridge costituisce la base di tutte le topologie presentate ed è mostrato in Figura 2.2. Esso è composto da due soli transistor, con i rispettivi diodi di ricircolo in antiparallelo, che permettono di produrre in uscita una tensione alternata a due livelli,

+Vin/2 e -Vin/2. Questa architettura a due livelli è molto usata per un accoppiamento perfetto con la PWM, dal momento che quest'ultima genera appunto proprio due livelli.

Figura 2.2 - Circuito di un inverter a mezzo ponte.

Il funzionamento è piuttosto semplice e dipende dallo stato dei transistor presenti, se accesi o spenti. Quindi in tutto sono possibili 4 stati, mostrati nella Tabella 2.1.

| S+  | S-  | STATO            | Vout   | Componenti ON               |

|-----|-----|------------------|--------|-----------------------------|

| ON  | ON  | X (indesiderato) | -      | -                           |

| ON  | OFF | 1                | Vdc/2  | S+ se iout>0, D+ se iout <0 |

| OFF | ON  | 2                | -Vdc/2 | D- se iout>0, S- se iout<0  |

| OFF | OFF | 3                | 0      | D- se iout>0, D+ se iout<0  |

Tabella 2.1 - Tabella rappresentativa degli stati assunti dal convertitore a mezzo ponte.

Nel caso in cui vengano accesi entrambi i transistor, si genera uno stato indesiderato che cortocircuita la sorgente DC. Perciò bisogna evitare, settando correttamente il driver, che il circuito finisca in questo stato.

Al contrario con S+ acceso e S- spento si ottiene sul carico una tensione di +Vin/2, dove il verso della corrente iout dipende da quale componente conduce. Infatti, se S+ conduce, la corrente ha verso positivo, se invece è D+ a condurre, sarà negativa.

Invece con S+ spento e S- acceso si ha in uscita una tensione di -Vin/2 con la corrente che può scorrere in entrambi i versi in base al dispositivo che conduce come mostrato nella tabella.

Infine, se entrambi i transistor S+ e S- sono spenti, la corrente, a seconda del verso, scorre su uno dei due diodi, generando la tensione in uscita di una determinata polarità. Nel caso iout sia positiva scorrerebbe su D- e si avrebbe sul carico +Vin/2, mentre se la corrente fosse negativa passerebbe su D+, provocando sul carico una tensione di -Vin/2.

Questo circuito fornisce il punto di partenza per le altre architetture descritte successivamente, ponendo le basi sul funzionamento e sul comportamento della tensione in uscita. Quest'ultima è perciò una tensione alternata dato che, presa una corrente continua in ingresso, si genera una tensione a più livelli sul carico. Il carico varia in base agli utilizzi e potrebbe essere composto da componenti puramente resistivi oppure sia resistivi che reattivi, come l'altoparlante di Figura 1.3.

# 2.2 VANTAGGI DELL'ARCHITETTURA MULTILIVELLO

Il circuito tipico realizzativo di un inverter è il mezzo-ponte descritto nel paragrafo precedente e rappresenta un esempio di inverter a due livelli, quindi l'uscita è descritta utilizzando due diversi livelli di tensione: +Vdc/2 e -Vdc/2. Successivamente sono state sviluppate anche topologie che presentano un maggior numero di livelli, di cui le più utilizzate verranno descritte nel paragrafo successivo, che offrono vantaggi e svantaggi rispetto a questa architettura [5].

Innanzitutto, gli inverter multilivello consentono di superare i limiti sulle tensioni massime applicabili al sistema di conversione, altrimenti imposti dai valori massimi applicabili ai singoli dispositivi di potenza utilizzati. Questo significa che lo stress di tensione sul singolo dispositivo, rispetto al totale in uscita, è molto minore e si può generare una tensione maggiore. Pertanto, permettono la realizzazione di apparati che possono essere collegati alle reti di distribuzione in media tensione senza l'interposizione di trasformatori, oppure alimentare grandi macchine elettriche rotanti di decine e

centinaia di kW, quali i motori dei locomotori o di grandi impianti industriali, i generatori eolici ecc.

Se da un lato i convertitori multilivello superano i vincoli sulle tensioni massime ai morsetti, dall'altro, essi danno luogo ad una considerevole riduzione sia del contenuto armonico nelle grandezze elettriche in uscita e in ingresso, sia della frequenza di commutazione dei dispositivi a semiconduttore impiegati, che consente di ridurre le perdite di commutazione. Ciò permette di ottenere significativi incrementi di efficienza ed una riduzione delle dimensioni o la totale eliminazione dei filtri in uscita e/o in ingresso. Infatti, le tensioni presenti ai morsetti di uscita dell'inverter presentano forme d'onda che si possono approssimare a delle sinusoidi, inoltre hanno un basso contenuto di armoniche di tensione e corrente.

La possibilità di utilizzare dispositivi di potenza a bassa tensione (relativamente alle tensioni ai morsetti) incrementa ulteriormente i vantaggi in quanto essi hanno bassissime resistenze di conduzione e, operando a frequenze più basse, sono affetti da perdite per commutazione trascurabili o minime.

Da tutto ciò, derivano ulteriori vantaggi: per esempio, i dissipatori termici e i filtri in ingresso e/o in uscita sono notevolmente più piccoli, quindi i convertitori sono più compatti e leggeri e i materiali isolanti sono soggetti a tensioni e frequenze più basse, quindi a stress inferiori, a tutto vantaggio dell'affidabilità e della durata all'intero sistema. Ovviamente, il prezzo da pagare è una maggiore complessità dei circuiti, infatti sono necessari molti più componenti e un sistema di pilotaggio maggiormente difficoltoso, difficoltà che cresce in modo più che lineare con il numero di livelli scelto.

Infine, un'altra caratteristica degli inverter multilivello è la possibile presenza di stati ridondanti, cioè più combinazioni di pilotaggio dei transistor che portano ad avere la stessa tensione di uscita, cosa che permette ad esempio di creare un sistema tollerante agli errori.

### 2.3 TIPOLOGIE

Nella letteratura sono descritte molte tipologie [6, 7, 8] sviluppate nel corso degli anni e queste si differenziano tra loro per numero di componenti, numero di sorgenti in DC e caratteristiche di funzionamento.

Le architetture più utilizzate e più note al momento sono il diode clamped inverter, il floating capacitor inverter e il cascaded H-bridge inverter, ma numerose altre sono state sviluppate e sono in fase di studio, promettendo numerosi vantaggi su più punti di vista, come la riduzione del numero di componenti, cosa che promette l'inverter T-Type, presentato nel paragrafo 2.3.4 e rappresentante delle nuove topologie in corso di perfezionamento.

### 2.3.1 DIODE CLAMPED INVERTER

Questa configurazione è stata proposta nel 1981 da Nabae [9] e viene anche chiamata 'neutral point clamped'. Questo nome deriva dal fatto che presenta un 'neutral point', cioè una connessione ad un punto a tensione nulla. Questo punto, in aggiunta al DC-bus, permette di creare più livelli in uscita, dove il DC-bus è in genere costituito da un numero pari di condensatori, i quali permettono di suddividere la tensione di ingresso. Inoltre, utilizzano anche numerosi diodi di 'clamping', che sono diodi che permettono il passaggio della corrente dall'ingresso all'uscita e di bloccare un certo livello di tensione.

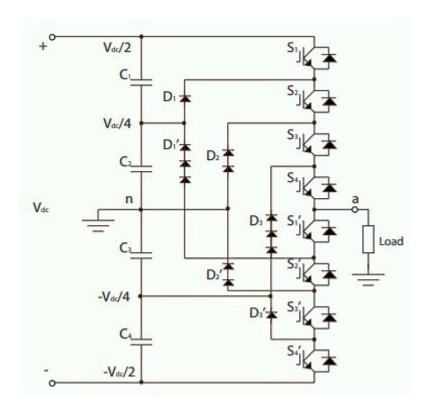

La struttura tipica di un inverter a cinque livelli è rappresentata in Figura 2.3.

Figura 2.3 - Circuito del diode clamped inverter.

Questa consiste di quattro condensatori e otto interruttori, necessari per generare i cinque livelli della tensione di uscita. Infatti, generalizzando per un inverter a n livelli, servono (n-1) condensatori, in modo da suddividere l'ingresso in (n-1) parti e ai quali si aggiunge il livello zero, dato dal punto neutro. Oltre a questo, sono presenti (2n-1) interruttori e la tensione che ognuno di loro deve sopportare è pari a 2Vdc/(n-1). Ad ogni modo, un problema che non esiste nell'inverter a due livelli e che invece si presenta in questa configurazione è la necessità di assicurarsi che la tensione tra i due (o (n-1) nel caso di n livelli) condensatori in serie del bus di ingresso sia equilibrata.

In questa topologia, come in quelle che vedremo successivamente, la funzione di interruttore viene realizzata da degli IGBT, ai quali è collegato un diodo in antiparallelo, necessario in quanto il dispositivo può essere danneggiato definitivamente quando in esso viene forzata una corrente inversa.

La caratteristica principale di questa architettura è la numerosa presenza di diodi di clamping che sono però soggetti a stress ad alta tensione pari a Vdc(n-2) /(n-1). Di conseguenza, è richiesto il collegamento in serie dei diodi, in cui il numero di diodi richiesto sarà di (n-1) \*(n-2), in modo da ridurre il carico di tensione sul singolo componente.

Per avere cinque possibili livelli di tensione sui rami dell'inverter, gli IGBT sono controllati in modo tale che in ogni momento solo quattro degli otto interruttori siano in conduzione, tenendo in considerazione che in un ciclo completo un interruttore può commutare una sola volta.

La Tabella 2.2 presenta tutti gli stati possibili, attraverso i transistor nella parte superiore S1, S2, S3, S4, dato che i corrispondenti interruttori nella parte inferiore S1', S2', S3', S4' hanno un comportamento opposto. Sotto ogni colonna degli interruttori vengono inseriti degli 1 e 0 che segnalano se sono accesi o spenti: un 1 indica che l'interruttore viene acceso ma non obbligatoriamente conduce, infatti, in base al verso della corrente, conduce il transistor o il suo diodo di ricircolo. Uno 0 segnala al contrario che il l'interruttore è spento. Questo schema è poi utilizzato anche per le architetture che seguono.

Nella tabella sono presenti tutte le 16 combinazioni possibili di funzionamento del circuito al variare del pilotaggio. Tra queste, solo cinque producono stati ammissibili e

sono corrispondenti ai livelli di tensione possibili in uscita:-Vdc/2, -Vdc/4, 0, Vdc/4 e Vdc/2.

Nelle altre situazioni si hanno invece degli stati cosiddetti 'proibiti', così definiti per il fatto che la tensione di uscita cambia al variare del verso della corrente, perciò non possono essere utilizzati nel pilotaggio per via di questa indeterminatezza. Negli stati definiti ammissibili, al contrario, ciò non avviene.

| S1 | S2 | S3 | S4 | Vo             |

|----|----|----|----|----------------|

| 0  | 0  | 0  | 0  | -Vdc/2         |

| 0  | 0  | 0  | 1  | -Vdc/4         |

| 0  | 0  | 1  | 0  | Stato proibito |

| 0  | 0  | 1  | 1  | 0              |

| 0  | 1  | 0  | 0  | Stato proibito |

| 0  | 1  | 0  | 1  | Stato proibito |

| 0  | 1  | 1  | 0  | Stato proibito |

| 0  | 1  | 1  | 1  | Vdc/4          |

| 1  | 0  | 0  | 0  | Stato proibito |

| 1  | 0  | 0  | 1  | Stato proibito |

| 1  | 0  | 1  | 0  | Stato proibito |

| 1  | 0  | 1  | 1  | Stato proibito |

| 1  | 1  | 0  | 0  | Stato proibito |

| 1  | 1  | 0  | 1  | Stato proibito |

| 1  | 1  | 1  | 0  | Stato proibito |

| 1  | 1  | 1  | 1  | Vdc/2          |

Tabella 2.2 - Tabella rappresentativa degli stati assunti dal diode clamped inverter.

Procedendo alla descrizione del funzionamento, iniziamo con lo stato –Vdc/2. Questi è ottenuto spegnendo i quattro transistor nella parte superiore S1, S2, S3 e S4, e di conseguenza accendendo i quattro nella parte inferiore, S1', S2', S3', S4'.

In questo modo si ottiene un percorso conduttivo attraverso i quattro transistor, o i rispettivi diodi di ricircolo, che connette il punto a tensione –Vdc/2 dell'ingresso all'uscita. Infatti, nel caso di corrente entrante nel carico, questa circola attraverso i diodi di ricircolo dei transistor nella parte inferiore, ottenendo in uscita proprio –Vdc/2. Ciò che lo rende uno stato utilizzabile è il fatto che, avendo una corrente di verso opposto al precedente, perciò uscente dal carico, si ottiene ancora la stessa tensione, con l'unica differenza data da quali dispositivi conducono. Altrimenti si ha infatti passaggio di corrente attraverso gli interruttori S1', S2', S3', S4'.

Se invece abbiamo accesi S4, S1', S2' e S3' si ha un nuovo stato utilizzabile in uscita, corrispondente al livello di tensione –Vdc/4. Il percorso della corrente è infatti ininfluente ai termini del potenziale di uscita e, nel caso di corrente entrante, essa fluisce attraverso C1, C2, C3, D3 e S4. Al contrario, con la corrente uscente, scorre sui diodi di ricircolo di S1', S2', S3' e D3' e C4.

Un terzo stato lecito si ha accendendo i quattro transistor centrali S3, S4, S1', S2' e provoca una tensione nulla sul carico, connettendo l'uscita con il neutro presente nel circuito. Nel caso di corrente entrante, essa passa per C1, C2, D2, S3 e S4, creando un percorso connettivo con il carico. Se invece la corrente è uscente, passa attraverso S1', S2', D2', C3 e C4.

Il penultimo stato possibile è rappresentato da Vdc/4 che si ottiene dando un ingresso alto ai transistor S2, S3, S4, S1', in questo modo si fraziona la tensione attraverso il condensatore C1 e si ottiene il livello desiderato di tensione. Analizzando lo scorrimento della corrente, se essa scorre con verso entrante, allora conducono C1, D1, S2, S3, S4, in modo da unire l'ingresso con l'uscita. Nel caso opposto di corrente uscente dal carico si troveranno a condurre invece S1', D1', C2, C3 e C4.

L'ultimo stato ottenibile in uscita corrisponde a Vdc/2, facendo di esso il valore più alto possibile. Per raggiungere questo livello di tensione occorre accendere i transistor S1, S2, S3 e S4, cioè quelli nella parte superiore, tenendo invece spenti quelli inferiori. La corrente si trova quindi a scorrere, nel caso di corrente verso il carico, attraverso S1, S2, S3, S4; quando la corrente scorre invece nel verso opposto, passa per i diodi di ricircolo dei transistor superiori e poi nei condensatori C1, C2, C3 e C4, dato che rappresenta il massimo raggiungibile.

Questa struttura presenta quindi una topologia piuttosto semplice, che presenta dei vantaggi e svantaggi nell'utilizzo, anche in base al numero di livelli richiesto per l'uscita.

Il maggiore beneficio è che, prevedendo per ogni ramo un numero doppio di interruttori rispetto al normale inverter a due livelli, ognuno di questi deve bloccare solo metà della tensione DC del bus di ingresso.

Inoltre, un altro punto di forza risiede nella semplicità costruttiva con pochi e robusti componenti allo stato solido (interruttori e diodi di ricircolo), nel limitato utilizzo di condensatori e nella costruzione modulare che permette l'accoppiamento back to back.

Lo svantaggio di questa topologia è nella difficoltà di correzione dinamica delle tensioni, nella mancanza di stati ridondanti, in una certa complessità della modulazione e nell'elevato numero di componenti nel caso di un numero di livelli elevato, in particolare dei diodi di clamping. Riferendoci a questo, il numero di diodi aumenta nell'ordine di n², con n numero di livelli, e questo aumento esponenziale diventa impegnativo nel caso di numeri alti.

Riguardo il bilanciamento delle tensioni, il problema nasce quando i condensatori, posti nel DC-link, si trovano a trasferire delle potenze attive. Questo provoca cariche e scariche di essi non uguali, in parte a causa di diversi carichi di lavoro, oppure la corrente viene assorbita dai nodi tra i condensatori. Questo fatto può provocare tensioni dei condensatori diverse, che vanno necessariamente corrette allo scopo di mantenere un equilibrio.

Per risolvere il problema è possibile aggiungere un circuito di bilanciamento aggiuntivo o implementando metodi di controllo più complessi [10]. A causa delle complicazioni del bilanciamento della tensione del condensatore, questa topologia con un numero elevato di livelli di tensione è insolita. La presenza di eventuali stati ridondanti, cioè stati che forniscono la stessa tensione in uscita con combinazioni di pilotaggio diverse, permetterebbe di poter sistemare questo problema. Infatti, utilizzando combinazioni diverse si generano anche cariche e scariche diverse sui condensatori interessati, dando la possibilità, variando gli stati utilizzati ma lasciando invariata la tensione di uscita, di bilanciare le tensioni dei condensatori. Però questa soluzione non è utilizzabile per questa topologia data la mancanza di questi stati, mentre viene utilizzata per altre architetture.

#### 2.3.2 FLOATING CAPACITOR INVERTER

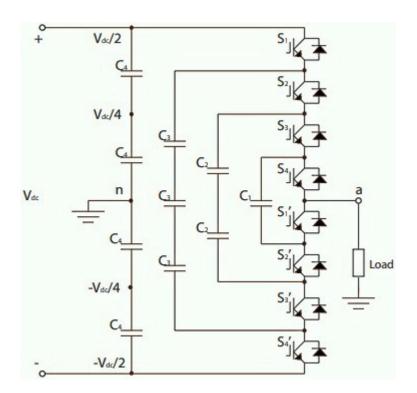

Questa topologia è stata sviluppata da Maynard [11] nel 1992 e presenta una struttura molto simile al diode clamping inverter, con delle opportune differenze.

La caratteristica principale è data dal fatto che la suddivisione della tensione in ingresso è effettuata attraverso dei condensatori flottanti rispetto al collegamento a massa, infatti sono in grado di caricarsi e in questo modo mantengono la tensione al valore desiderato. Questo permette in uscita la generazione dei diversi livelli, in base a quali condensatori vengono caricati.

Figura 2.4 - Circuito del floating capacitor inverter.

Questa architettura presenta (n-1) condensatori nel DC-bus condiviso, dove n è il numero di livelli dell'inverter, e vengono utilizzati 2(n-1) interruttori, con il proprio diodo di ricircolo, per permettere il passaggio della corrente in entrambi i versi. Questa rappresenta una caratteristica condivisa con la topologia mostrata nel paragrafo precedente ma, come grande differenza, utilizza dei condensatori al posto dei diodi e aumenta il numero di possibili combinazioni di commutazione poiché permettono il passaggio della corrente in entrambi i versi, cosa che non fanno i diodi. Si ottiene perciò che diversi stati di

commutazione saranno in grado di generare lo stesso livello di tensione generando una ridondanza che porta a diversi vantaggi. Bisogna tenere conto però, riguardo il dimensionamento e il numero dei componenti, che ogni condensatore deve mantenere una tensione pari a Vdc/(n-1) e quindi sarà necessario un numero molto elevato di capacità, rappresentato da n\*(n-1) /2.

In Figura 2.4 è mostrato lo schema di questo convertitore a cinque livelli, nella configurazione in cui presenta il punto a tensione nulla nel mezzo del DC-bus, come il diode clamping converter.

Questo circuito presenta, secondo ciò enunciato precedentemente, un DC-bus costituito da quattro condensatori, i quali suddividono l'ingresso potendo tenere ciascuno una tensione pari a Vdc/4. Inoltre, sono necessari anche otto interruttori, pilotati da un driver in modo da tenerne sempre accesi quattro, e sei condensatori, che permettono il passaggio della corrente dall'ingresso al carico. In questo modo si ottengono 16 possibili stati in uscita dalle combinazioni di accensione dei transistor e sono anche considerati tutti stati permessi. Infatti, non si presentano ambiguità di valori in uscita dovute al verso della corrente e si ha la presenza di molti stati ridondanti.

Ora procediamo alla descrizione degli stati ottenibili in uscita, mostrati nella Tabella 2.3, in cui è utilizzata la stessa metodologia della topologia prima analizzata.

Analizzando il comportamento al variare del pilotaggio, si osserva la presenza di diversi stati ridondanti per i livelli intermedi, mentre non sono presenti per i livelli esterni. Questo fatto non va però ad influire sul corretto bilanciamento delle tensioni nei condensatori, che verrà successivamente descritto.

In ogni stato qui rappresentato si può osservare un percorso conduttivo tra ingresso e uscita, che ora viene spiegato nel dettaglio per tutti i casi possibili, nell'ipotesi di corrente entrante nel carico. Questo poiché si tiene conto del fatto che, con corrente uscente, si ottiene lo stesso valore di tensione, dove l'unica differenza è data dall'inversione del comportamento dei condensatori; questo significa che, in base al verso della corrente, le capacità si caricano o si scaricano.

| S1 | S2 | S3 | S4 | Vo     |

|----|----|----|----|--------|

| 0  | 0  | 0  | 0  | -Vdc/2 |

| 0  | 0  | 0  | 1  | -Vdc/4 |

| 0  | 0  | 1  | 0  | -Vdc/4 |

| 0  | 0  | 1  | 1  | 0      |

| 0  | 1  | 0  | 0  | -Vdc/4 |

| 0  | 1  | 0  | 1  | 0      |

| 0  | 1  | 1  | 0  | 0      |

| 0  | 1  | 1  | 1  | Vdc/4  |

| 1  | 0  | 0  | 0  | -Vdc/4 |

| 1  | 0  | 0  | 1  | 0      |

| 1  | 0  | 1  | 0  | 0      |

| 1  | 0  | 1  | 1  | Vdc/4  |

| 1  | 1  | 0  | 0  | Vdc/4  |

| 1  | 1  | 0  | 1  | 0      |

| 1  | 1  | 1  | 0  | Vdc/4  |

| 1  | 1  | 1  | 1  | Vdc/2  |

Tabella 2.3 - Tabella rappresentativa degli stati assunti dal floating capacitor inverter.

- Stato 0000: Sono spenti gli interruttori nella parte superiore S1, S2, S3 e S4, mentre sono accesi quelli nella parte inferiore. Qui la corrente procede dal nodo inferiore a tensione -Vdc/2 direttamente nel carico attraverso i diodi di ricircolo di S1', S2', S3', S4', senza caricare o scaricare alcun condensatore. In questo modo si ottiene -Vdc/2 in uscita.

- Stato 0001: In questo stato sono accesi S4, S1', S2', S3' e si ha in uscita il valore di tensione –Vdc/4. Si ha il passaggio della corrente attraverso i diodi di ricircolo di S2', S3', S4' partendo dal nodo a –Vdc/2. Successivamente passa attraverso C1, che viene scaricata, e si guadagna il valore di tensione che si trovava su quel condensatore, corrispondente a Vdc/(m-1), che qui vale Vdc/4. Si ha ora la corrente sull'interruttore S4 e sul carico arriva una tensione di –Vdc/4.

- Stato 0010: Sono accesi S3, S1', S2' e S4' e in questo caso la corrente scorre sui condensatori C2 e C1. In particolare, C2 è costituito da due capacità che vengono scaricate, provocando un aumento di tensione pari a Vdc/2, mentre C1 viene caricata, diminuendo la tensione di Vdc/4. In uscita si ottiene infine il valore di –Vdc/4.

- Stato 0011: Gli interruttori S3, S4, S1', S2' sono accesi e generano in uscita una tensione nulla. Questo si ottiene poiché la corrente si trova a scaricare C2, passando su di esso e provoca un aumento della tensione di Vdc/2, infatti, partendo dal nodo –Vdc/2, grazie a questo guadagno, arriva al livello zero.

- Stato 0100: Sono accesi S2, S1', S3', S4' e si ha la corrente che scorre attraverso i condensatori C3 e C2. Questi ultimi vengono rispettivamente scaricati e caricati e generano in uscita la tensione –Vdc/4.

- Stato 0101: Gli interruttori S2, S4, S1', S3' sono accesi e in uscita si ha una tensione nulla provocata dalla scarica di C3 e C1 e la carica di C2. Questi cambiamenti combinati generano un aumento della tensione di Vdc/2 dall'iniziale -Vdc/2, in modo da avere livello nullo.

- Stato 0110: Sono accesi gli interruttori S2, S3, S1', S4' e provoca il passaggio della corrente che genera la tensione nulla all'uscita. Durante il transito sui dispositivi interessati, in questo caso C3 e C1, si osserva in uscita il livello zero di tensione. In particolare, C3 viene scaricata e C1 viene caricata e insieme producono un aumento della tensione pari a Vdc/2.

- Stato 0111: In questo stato si hanno S2, S3, S4, S1' accesi e si ha transito di corrente, partendo dal nodo d'ingresso a tensione –Vdc/2, attraverso C3, S2, S3 e S4 e durante il quale i condensatori vengono scaricati. Essendo ognuno di essi capace di contenere un valore pari a Vdc/4, si ottiene in uscita proprio il valore di Vdc/4.

- Stato 1000: Gli interruttori S1, S2', S3', S4' sono tenuti accesi e si ha in uscita il valore di –Vdc/4. Questo valore si ottiene poiché la corrente parte dal nodo d'ingresso a Vdc/2, da lì passa per l'interruttore S1 e va sui condensatori C3. Queste capacità vengono caricate e si ha una perdita di tensione equivalente a Vdc/4 per ognuno dei condensatori. Dato che sono presenti tre di essi in quel ramo si ha una perdita totale di 3Vdc/4.

- Stato 1001: Sono accesi S1, S4, S2', S3' in modo da avere passaggio di corrente su C3 e C1. Infatti, C3 si carica e C1 si scarica, in modo da produrre una perdita pari a Vdc/2 e, partendo da un valore di Vdc/2, si ha ai capi del carico una tensione nulla.

- Stato 1010: Gli interruttori S1, S3, S2', S4' sono accesi e ai capi del carico si ha la tensione nulla, poiché la corrente, partendo dal nodo a potenziale Vdc/2, si trova a scorrere attraverso C3, C1 e C2. Nel passaggio, C1 e C3 si caricano mentre C2 si scarica e si ha un calo di tensione di Vdc/2 che genera tensione nulla in uscita.

- Stato 1011: Gli interruttori S1, S3, S4, S2' sono accesi e la corrente segue un percorso che va dal potenziale Vdc/2 di ingresso al carico, attraversando i condensatori C3 e C2. Questi ultimi vengono rispettivamente caricati e scaricati producendo una tensione pari a Vdc/4 in uscita.

- Stato 1100: Gli interruttori S1, S2, S3', S4' sono accesi e in uscita si ha la tensione di Vdc/4. Questo è dovuto al fatto che C2 viene caricata e C1 scaricata e si ha una perdita di Vdc/4 dall'ingresso.

- Stato 1101: Gli interruttori S1, S2, S4, S3' sono accesi e si ha la corrente che passa attraverso C2, provocando la carica dei condensatori di questi. Nel passaggio si perde una tensione pari a Vdc/2 e in uscita si ha il livello neutro di tensione.

- Stato 1110: Gli interruttori S1, S2, S3, S4' sono accesi e si produce ai capi del carico una tensione pari a Vdc/4 poiché la corrente, partita dal nodo a potenziale Vdc/2, scorre lungo S1, S2, S3 e successivamente su C1. In questo passaggio questa capacità si carica e assorbe una tensione pari a Vdc/4.

- Stato 1111: Gli interruttori S1, S2, S3, S4 sono accesi e si ha un percorso diretto che collega il potenziale Vdc/2 al carico passando attraverso i transistori nella parte superiore, senza caricare o scaricare alcun condensatore. Infatti, si ottiene in uscita proprio Vdc/2, dato che non ci sono variazioni di tensione dovute alle capacità.

Sono quindi presenti molti stati ridondanti il cui scopo è quello di bilanciare le cariche sui condensatori. Infatti, per il corretto funzionamento del circuito è necessario che, effettuato un ciclo completo di commutazione, la variazione totale di tensione su un condensatore sia nulla. Questo si ottiene facendo in modo che in un ciclo intero avvenga lo stesso numero di cariche e scariche su ogni condensatore, in modo da mantenere la tensione media al valore desiderato, nel caso a cinque livelli corrispondente a Vdc/4.

In assenza di questi stati non si potrebbero infatti avere più combinazioni nel comportamento dei condensatori e si arriverebbe ad uno sbilanciamento della carica, al contrario, utilizzando metodi di pilotaggio diversi per produrre lo stesso stato all'interno di un ciclo, è permesso regolare il verso della corrente sui condensatori e quindi regolare le cariche e scariche di essi. Infatti, uno sbilanciamento della tensione produce

un'asimmetria che introduce componenti armoniche, maggiore tensione di blocco per gli interruttori di potenza e i diodi del convertitore.

Uno dei vantaggi di questa topologia è dato dal numero contenuto di elementi attivi presenti per un numero di livelli basso. Inoltre, l'utilizzo degli stati ridondanti permette un impiego equo di tutti gli interruttori e una modulazione semplice e robusta. I dispositivi sono anche attraversati da una corrente media molto simile e hanno anche una temperatura di regime simile.

Lo svantaggio principale risiede nel gran numero di condensatori necessari, e il fatto che la tensione ai loro capi debba essere molto stabile per un funzionamento affidabile e sono inoltre necessari circuiti correttivi della deriva. All'aumentare del numero di livelli è necessario un maggior numero di condensatori, pertanto le specifiche di questi ultimi dovranno essere sempre più stringenti. Inoltre, presenta anche un ingombro maggiore rispetto alla tipologia con i diodi di clamping, presentata nel paragrafo precedente.

## 2.3.3 CASCADED CELL MULTILEVEL INVERTER

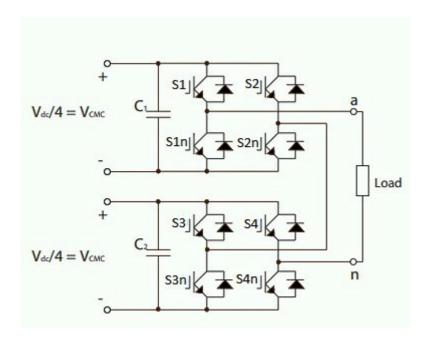

Una terza topologia qui descritta è rappresentata dal convertitore multilivello a celle in cascata [12] e presenta delle notevoli differenze rispetto ai due precedentemente descritti.

Innanzitutto, presenta una struttura modulare, dove ogni modulo è costituito da un inverter a ponte intero ed essi vengono posti in cascata, in modo da creare un convertitore multilivello. Infatti, replicando n-volte la cella costitutiva si ottiene un numero di livelli L=2n+1. Si nota quindi come ognuno di essi va ad aggiungere due livelli in uscita in aggiunta al livello nullo e il totale è sempre un numero dispari.

Una seconda differenza è la necessità di più sorgenti in DC separate e isolate, in particolare una per ogni cella del convertitore e questo è un fattore di cui tenere conto in quanto potrebbe impedirne l'uso in alcune applicazioni, favorendone invece per altre come i pannelli fotovoltaici e i generatori eolici.

Figura 2.5 - Circuito del cascaded cell inverter.

In Figura 2.5 è mostrato il convertitore a cinque livelli, costituito da due ponti interi connessi tra di loro in cascata e ognuno con la propria alimentazione pari a Vdc/4. L'uscita totale di tensione è la somma di quelle dei singoli moduli e, considerando che un singolo stadio può produrre tre diversi valori di tensione Vdc/4, 0, -Vdc/4, questa può oscillare tra Vdc/2 e –Vdc/2 con un passo di Vdc/4, ottenendo proprio cinque livelli di tensione.

Generalizzando, questa architettura a n livelli ha (n-1) /2 stadi, corrispondenti a 4n interruttori, e presenta n sorgenti DC isolate. Inoltre, questa caratteristica di sommare le tensioni dei vari stadi in cascata permette di ottenere in uscita livelli di tensione regolabili a piacere, solo differenziando la tensione dell'alimentazione delle singole celle.

Ritornando al caso a cinque livelli con i due stadi in cascata, in ogni momento sono accesi quattro transistor, due per ogni modulo, e per passare da uno stato all'altro è sufficiente accendere un interruttore e/o spegnerne un altro, ottenendo in questo modo un totale di 16 stati possibili, mostrati nella Tabella 2.4. Il funzionamento di ogni modulo è descritto dalla Tabella 1.1 e quindi in ogni ramo è acceso solo un interruttore per volta, ad esempio se S1 è spento si ha S1n acceso, e le tensioni V1 e V2 rappresentano rispettivamente le uscite del primo e del secondo stadio, mentre Vo è la somma delle due.

| Stato | S1  | S2  | S3  | S4  | V1     | V2     | Vo     |

|-------|-----|-----|-----|-----|--------|--------|--------|

| 0000  | OFF | OFF | OFF | OFF | 0      | 0      | 0      |

| 0001  | OFF | OFF | OFF | ON  | 0      | -Vdc/4 | -Vdc/4 |

| 0010  | OFF | OFF | ON  | OFF | 0      | +Vdc/4 | +Vdc/4 |

| 0011  | OFF | OFF | ON  | ON  | 0      | 0      | 0      |

| 0100  | OFF | ON  | OFF | OFF | -Vdc/4 | 0      | -Vdc/4 |

| 0101  | OFF | ON  | OFF | ON  | -Vdc/4 | -Vdc/4 | -Vdc/2 |

| 0110  | OFF | ON  | ON  | OFF | -Vdc/4 | +Vdc/4 | 0      |

| 0111  | OFF | ON  | ON  | ON  | -Vdc/4 | 0      | -Vdc/4 |

| 1000  | ON  | OFF | OFF | OFF | +Vdc/4 | 0      | +Vdc/4 |

| 1001  | ON  | OFF | OFF | ON  | +Vdc/4 | -Vdc/4 | 0      |

| 1010  | ON  | OFF | ON  | OFF | +Vdc/4 | +Vdc/4 | +Vdc/2 |

| 1011  | ON  | OFF | ON  | ON  | +Vdc/4 | 0      | +Vdc/4 |

| 1100  | ON  | ON  | OFF | OFF | 0      | 0      | 0      |

| 1101  | ON  | ON  | OFF | ON  | 0      | -Vdc/4 | -Vdc/4 |

| 1110  | ON  | ON  | ON  | OFF | 0      | +Vdc/4 | +Vdc/4 |

| 1111  | ON  | ON  | ON  | ON  | 0      | 0      | 0      |

Tabella 2.4 - Tabella rappresentativa degli stati assunti dal cascaded cell inverter.

Qui sono elencati tutti gli stati possibili ottenuti dalle combinazioni delle uscite dei singoli stadi e si ottengono numerosi stati ridondanti per i livelli intermedi, cioè tutti esclusi +Vdc/4 e –Vdc/4, rendendo più semplice il pilotaggio.

L'uscita totale è data dalla somma delle uscite dei singoli stadi, come si evidenzia nella tabella, quindi per ottenere il livello +Vdc/2 è necessario che entrambi i ponti generino una tensione di +Vdc/4 in uscita. Questa cosa avviene nel caso in cui S1 è acceso e S2 è spento nel primo stadio e S3 acceso e S4 spento nel secondo.

Per avere il livello –Vdc/2 serve invece tenere acceso S2 e spento S1 nel primo ponte e S4 acceso e S3 spento nel secondo, in modo da avere all'uscita di ogni stadio una tensione di –Vdc/4, che sommata tra tutte genera proprio –Vdc/2.

Nei casi intermedi, come detto, si hanno numerose combinazioni possibili e per avere il livello +Vdc/4 bisogna che uno dei due stadi produca una tensione pari proprio a +Vdc/4, mentre l'altro una tensione nulla. Stessa cosa si ha per il livello –Vdc/4, in cui ancora una

volta è sufficiente avere da uno dei due la tensione –Vdc/4, dove l'altro genera il livello zero.

Infine, il livello di tensione nullo può essere generato in due diversi modi: il primo consiste in entrambi i ponti che producono in uscita proprio una tensione pari a zero, cosa che si ottiene con entrambi gli interruttori superiori o inferiori accesi, oppure il secondo metodo è il risultato di uno dei due stadi che produce in uscita il livello +Vdc/4, mentre l'altro -Vdc/4, in modo che, sommandosi, si ha proprio il livello nullo.

Questa tipologia presenta come vantaggio la perfetta modularità con cui si presta per un uso in larga scala e con un numero elevato di livelli. Infatti, nelle due architetture precedentemente presentate, la crescita del numero di componenti al variare del numero di livelli era esponenziale mentre ora il rapporto è lineare, permettendo un notevole guadagno nella quantità di dispositivi necessari per la costruzione, anche se sono necessarie più sorgenti di tensione.

Una ulteriore peculiarità di questo circuito è il fatto di poter ottenere in uscita tensioni maggiori di quelle del DC-link, sfruttando il fatto che i livelli di tensione finali si ottengono come somma dei singoli stadi. Ad esempio, nel nostro caso a cinque livelli ogni modulo ha un'alimentazione pari a Vdc/4 e in uscita si riescono ad avere tensioni di ± Vdc/2.

Presenta come svantaggio il bisogno di più sorgenti in DC isolate per motivi di bilanciamento della tensione, infatti, sono necessarie in modo che possano ricaricare sempre i condensatori presenti nel DC-link. Perciò presenta come campo principale di applicazione quello delle energie rinnovabili, dove è possibile isolare tutte le fonti di tensione.

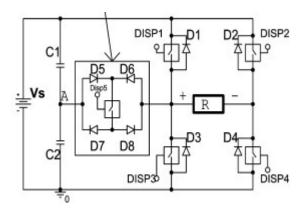

#### 2.3.4 INVERTER T-TYPE

Negli ultimi anni è apparsa in letteratura una nuova tipologia di inverter con l'obiettivo primario di ridurre al minimo il numero di interruttori necessari per realizzarlo. Questa architettura, chiamata T-type, è stata presentata da Ceglia in [4] ed è anche quella utilizzata per la realizzazione dell'inverter sviluppato in questa tesi, attraverso la piattaforma Simulink, e che viene mostrata nel paragrafo 5.1.

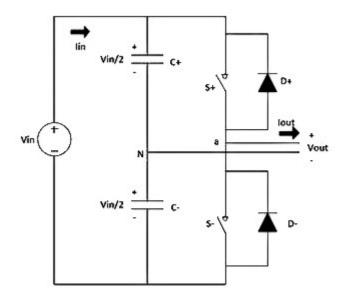

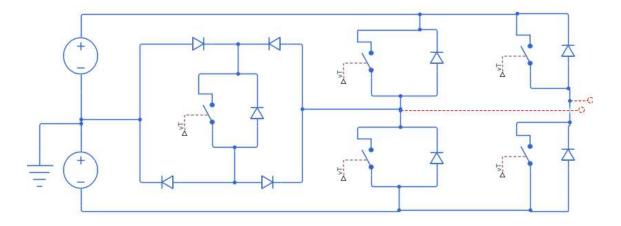

Figura 2.6 - Circuito dell'inverter T-Type.

Questa architettura, mostrata in Figura 2.6, è costituita da un interruttore bidirezionale in corrente e bidirezionale nel bloccaggio delle tensioni, qui chiamato Disp5, e da quattro interruttori bidirezionali in corrente e unidirezionali nel bloccaggio, rappresentati da Disp1, Disp2, Disp3 e Disp4. Si può anche vedere come un ponte intero a tre livelli, con il carico posto tra i due bracci di esso, e un ulteriore interruttore bidirezionale che permette di aggiungere due livelli alla tensione di uscita.

Questo circuito è dunque molto semplice e presenta in uscita cinque livelli:  $\pm Vs$ ,  $\pm Vs/2$ , 0, ottenibili con una opportuna configurazione, presentando però il limite della mancanza di stati ridondanti, problema che potrebbe provocare uno sbilanciamento della tensione sui condensatori nel DC-link. In ogni momento sono accesi sempre due interruttori, dove per passare da uno stato all'altro è sufficiente spegnerne uno ed accenderne un altro. Gli stati sono mostrati nella Tabella 2.5.

| Stati | Disp1 | Disp2 | Disp3 | Disp4 | Disp5 | Vo    |

|-------|-------|-------|-------|-------|-------|-------|

| 1     | ON    | OFF   | OFF   | ON    | OFF   | Vs    |

| 2     | OFF   | OFF   | OFF   | ON    | ON    | Vs/2  |

| 3     | OFF   | OFF   | ON    | ON    | OFF   | 0     |

| 4     | OFF   | ON    | OFF   | OFF   | ON    | -Vs/2 |

| 5     | OFF   | ON    | ON    | OFF   | OFF   | -Vs   |

Tabella 2.5 - Tabella rappresentativa degli stati assunti dall'inverter T-Type.

- Stato 1: Questo è lo stato che genera il massimo valore positivo, Vs. Sono accesi Disp1, che connette il terminale positivo del carico al nodo a potenziale Vs, e Disp4, che invece unisce il terminale negativo del carico alla massa. Si ha quindi passaggio di corrente, nel caso di corrente entrante nel terminale positivo del carico, attraverso Disp1 e Disp4. Nel caso di direzione opposta scorre invece sui corrispondenti diodi di ricircolo, D1 e D4.

- Stato 2: Stato che produce il livello Vs/2. L'interruttore ausiliario Disp5 è acceso, collegando il terminale positivo del carico al punto A, e Disp4 pure è acceso, creando un collegamento tra il terminale negativo del carico e la terra, mentre tutti gli altri interruttori controllati sono spenti. La corrente scorre, nel caso di corrente entrante al nodo positivo del carico, attraverso D5, Disp5, D8 e Disp4; nella direzione opposta invece passa su D4, D6, Disp5 e D7.

- Stato 3: Sono accesi Disp3 e Disp4 e il carico viene cortocircuitato con la terra, ottenendo in uscita il livello neutro di tensione. La corrente si trova a scorrere attraverso i due interruttori che sono accesi.

- Stato 4: Questo stato produce in uscita la tensione –Vs/2. L'interruttore ausiliario Disp5 viene acceso, connettendo il terminale positivo del carico al punto A, insieme a Disp2, che connette il carico al nodo a potenziale –Vs. La corrente scorre in un verso attraverso Disp2, D6, Disp5 e D7; altrimenti passa su D5, Disp5, D8 e D2.

- Stato 5: Genera la massima tensione negativa, -Vs. Sono accesi Disp2, che connette il terminale negativo del carico a Vs, e Disp3, che invece unisce il terminale positivo del carico alla terra. I dispositivi che conducono sono, nel caso di corrente entrante nel carico, Disp2 e Disp3, mentre nella direzione opposta sono i rispettivi diodi di ricircolo D2 e D3.

In questa configurazione i due condensatori, predisposti alla divisione della tensione iniziale, sono connessi direttamente al DC-bus e, poiché tutte le combinazioni di commutazione sono utilizzate in un unico ciclo, l'equilibrio dinamico di tensione tra i due condensatori viene ripristinato automaticamente.

Ha come grande vantaggio il ridotto numero di interruttori, evidente nel circuito mostrato nel caso a cinque livelli, che si aggiunge inoltre al ridotto numero di diodi e capacità richieste, soprattutto se riferito in confronto alle tipologie precedentemente presentate.

# III MODULAZIONE SIGMA-DELTA

Ora procediamo con la trattazione di una delle tecniche di modulazione maggiormente usate, la modulazione sigma-delta [13, 14], che viene utilizzata per effettuare il pilotaggio dell'inverter multilivello testato.

Questa tecnica ha visto accrescere il proprio utilizzo in una vasta gamma di componenti elettronici moderni, come convertitori analogico-digitali, i sintetizzatori di frequenza, gli alimentatori switched, e il controllo dei motori.

Qui viene svolta innanzitutto una introduzione generale in cui si spiega cos'è e quali vantaggi propone, per poi passare alla descrizione dei circuiti del primo ordine e degli ordini successivi.

#### 3.1 INTRODUZIONE AL SIGMA-DELTA

La modulazione sigma-delta è una tecnica sviluppata nei primi anni '60 per rappresentare un convertitore analogico-digitale o digitale-analogico che sfruttava il sovracampionamento e il noise-shaping.

Il sovracampionamento consiste nel far lavorare il modulatore ad una frequenza superiore a quella del segnale entrante, in genere tra 48 e 512 volte maggiore, e produce dei vantaggi rispetto alla conversione fatta alla frequenza di Nyquist. Infatti, come mostrato nella Figura 3.1, si ha la stessa potenza di rumore per entrambi, ma ora è spalmata su una banda maggiore, migliorando la risoluzione e il rapporto segnale-rumore.

Figura 3.1 - Densità spettrale di potenza del rumore di quantizzazione per una conversione PCM alla frequenza di Nyquist e con sovracampionamento.

Oltre al sovracampionamento abbiamo anche parlato del noise-shaping, che rappresenta la caratteristica principale di questo modulatore. Questa tecnica consiste nel produrre una funzione di trasferimento del segnale, anche chiamata STF, e una del rumore, o NTF, in modo da mantenere inalterato il segnale e modellare lo spettro del rumore. Infatti, il rumore viene attenuato nella banda del segnale e amplificato fuori dalla banda.

Il modello generale di questa modulazione si può vedere in Figura 3.2 [15] ed è costituito da un ingresso u che entra in un sistema lineare, in genere costituito da uno o più integratori, insieme all'uscita retroazionata, producendo un segnale x. Questi viene poi quantizzato da un apposito circuito, producendo un segnale tipicamente su due livelli, quindi rappresentabile con un solo bit, e si ottiene l'uscita y.

La retroazione svolge un compito molto importante poiché permette di migliorare la risoluzione e le prestazioni migliorano al crescere del fattore di sovracampionamento.

Figura 3.2 - Modello generale del sigma-delta.

Gli ADC e i DAC basati sul sigma-delta hanno raggiunto livelli eccezionali di prestazioni in alta risoluzione e applicazioni a bassa velocità ma hanno avuto meno successo in applicazioni ad alta velocità. La principale barriera all'uso delle tecniche di noise-shaping ad alta frequenza è data dal fatto che la frequenza di campionamento, o clock, deve essere molte volte superiore alla frequenza di interesse, cosa che la tecnologia esistente spesso non permette. La necessità di un elevato rapporto di sovracampionamento può essere alleviata in qualche modo usando un modulatore di ordine elevato, ma questo non sempre è possibile poiché le simulazioni rivelano che i modulatori che presentano funzioni di trasferimento del rumore, o NTF, di ordini elevati spesso sono instabili. Perciò occorre scegliere accuratamente l'architettura e i relativi coefficienti ed effettuare continue

simulazioni, dato che al momento ancora non è stata sviluppata una legge generale per verificare la stabilità.

#### 3.2 MODULAZIONE SIGMA-DELTA DEL PRIMO ORDINE

L'architettura tipica di un modulatore sigma-delta del primo ordine è mostrata in Figura 3.3 [13]. Qui si trova lo schema di un convertitore analogico-digitale, ma può essere utilizzato anche in modo totalmente digitale, come avviene in questa tesi, semplicemente eliminando il DAC nella retroazione e dando in ingresso un segnale digitale.

Figura 3.3 - Convertitore A/D con modulatore sigma-delta del primo ordine.

Il modulatore consiste di un integratore a tempo discreto, un quantizzatore ed un eventuale convertitore digitale-analogico in retroazione. Il segnale che viene quantizzato non è perciò l'ingresso x[n] ma una versione filtrata della differenza tra l'ingresso ed una rappresentazione analogica ya[n] dell'uscita quantizzata y[n]. Il filtro, detto feedforward loop filter, è un integratore a tempo discreto la cui funzione di trasferimento è  $z^{-1}/(1-z^{-1})$ . Considerando il DAC ideale, allora può essere sostituito da una funzione di trasferimento unitaria, in modo da avere l'uscita del modulatore Y(z) data da:

$$Y(z)=X(z) z^{-1}+ E(z) (1-z^{-1})$$

(3.1)

Da questa formula si possono poi ricavare le funzioni di trasferimento del segnale e del rumore, che risultano STF=  $z^{-1}$  e NTF=  $1-z^{-1}$ . La funzione del rumore di quantizzazione risulta quindi avere un comportamento passa alto, come evidenziato dalla Figura 3.4, in cui è rappresentata questa funzione, prima in scala lineare e poi in scala logaritmica, comparata con quella dei convertitori PCM con sovracampionamento.

Figura 3.4 - NTF sigma-delta primo ordine: scala lineare (a), logaritmica in dB (b).

Figura 3.5 - Densità spettrale di potenza del rumore di quantizzazione per una conversione PCM alla frequenza di Nyquist e per una conversione PCM con sovracampionamento e noise-shaping.

L'effetto di tutto ciò è rappresentato dal noise-shaping, che in questo caso produce uno spettro di rumore molto attenuato nella banda del rumore, come visualizzato in Figura 3.5.

Analizzato lo spettro del rumore, si può ora procedere allo studio delle prestazioni di questo modulatore, considerando però il DAC come perfettamente lineare. Infatti, una eventuale non linearità potrebbe essere modellata come una sorgente di rumore che si somma direttamente all'ingresso, non venendo quindi influenzata dal noise-shaping.

Considerando inoltre come formule per STF e NTF rispettivamente  $z^{-1}$  e  $(1-z^{-1})$ , come precedentemente definito, si ha che la potenza del rumore in banda utile ha come formula:

$$\sigma_{ey} = \sigma_e^2 \frac{\pi^2}{3} \left(\frac{2f_s}{f_s}\right)^3 \tag{3.2}$$

Si ottiene quindi anche il modo per calcolare il rapporto segnale rumore o SNR:

$$SNR = 10\log(\sigma_x^2) - 10\log(\sigma_e^2) - 10\log\left(\frac{\pi^2}{3}\right) + 30\log\left(\frac{f_s}{2f_B}\right) =$$

$$= 10\log(\sigma_x^2) - 10\log(\sigma_e^2) - 10\log\left(\frac{\pi^2}{3}\right) + 9.03r(dB). \tag{3.3}$$

Si vede che ad ogni raddoppio della frequenza di campionamento questo rapporto migliora di 9 dB, cioè la risoluzione aumenta di 1+½ bit.

#### 3.3 MODULAZIONE SIGMA-DELTA DI ORDINE SUPERIORE

A partire dal modulatore del primo ordine è possibile anche ottenere dei circuiti più complessi, in cui possono essere presenti più integratori o anche più quantizzatori. In particolare, viene definito ordine di un modulatore il numero di zeri che presenta la funzione di trasferimento del rumore e, riferendoci al circuito del modulatore del primo ordine in Figura 3.3, ogni integratore corrisponde ad uno zero, perciò, considerando quell'architettura, occorre aggiungere degli integratori per aumentare l'ordine, come si può vedere dalla Figura 3.6 in cui viene rappresentato un modulatore del secondo ordine.

Figura - 3.6: Modulatore sigma-delta del secondo ordine.

Architetture di ordine superiore al primo permettono di avere dei vantaggi e degli svantaggi ed è una opzione da valutare in base alle necessità. Innanzitutto, ogni aumento corrisponde ad una risoluzione migliore a parità di fattore di interpolazione, oppure si può anche vedere come una diminuzione della frequenza di campionamento necessaria a parità di risoluzione. Presenta però come grosso svantaggio, a partire dal terzo ordine, il problema della stabilità. Questo problema consiste nel fatto che, dato un ingresso troppo elevato, il sistema può diventare instabile e comportarsi in modo non voluto, perciò è assolutamente fondamentale verificare che il modulatore sia stabile per poter funzionare correttamente.

Tornando alle formule, in sistemi di ordine superiore l'equazione (3.1) diventa:

$$Y(z)=X(z) z^{-1}+E(z) (1-z^{-1})^{L}$$

(3.4)

Quindi la funzione di trasferimento del segnale diventa pari a z<sup>-(L-1)</sup>, mentre la NTF invece sarà (1-z<sup>-1</sup>) <sup>L</sup>, con L ordine del modulatore. In particolare, questo fornisce una maggiore attenuazione del rumore di quantizzazione nella banda del segnale alle basse frequenze ed una maggiore amplificazione del rumore al di fuori della banda del segnale. Rispetto ad un sigma–delta del primo ordine, una parte maggiore di potenza del rumore è spinta fuori dalla banda utile, come si nota nei grafici di Figura 3.7 rappresentanti l'NTF del primo, secondo e terzo ordine.

Inoltre, cambiare l'ordine va a modificare anche la formula del rapporto segnale-rumore, dal momento che cambia lo spettro del rumore, e diventa nella sua forma generale:

$$SNR = 10\log(\sigma_x^2) - 10\log(\sigma_e^2) - 10\log\left(\frac{\pi^{2L}}{2L+1}\right) + (20L+10)\log\left(\frac{f_s}{2f_B}\right)(dB)$$

(3.5)

Da questa formula si nota come ora raddoppiando il fattore di sovracampionamento si ottiene un miglioramento di (6L+3) db di SNR, equivalenti a (L+ ½) bit di risoluzione. Si può anche vedere il massimo SNR raggiungibile in funzione dell'OSR, però in forma teorica, in Figura 3.8, dove si intende forma teorica poiché, per ordini superiori al secondo, per raggiungerla occorre un posizionamento degli zeri della NTF che porta all'instabilità.

Figura 3.7 - NTF per modulatori sigma-delta dal I al III ordine: spettri di ampiezza su scala lineare a confronto con la NTF del convertitore PCM a sovracampionamento con guadagno unitario; (a) scala lineare, (b) scala logaritmica in dB.

Figura 3.8 - SNR teorico per modulatore di ordine n.

# IV ARCHITETTURA DEL MODULATORE SIGMA-DELTA

Il modulatore sigma-delta, utilizzato qui per il pilotaggio dell'amplificatore audio, presenta ora, al contrario di quello mostrato nel paragrafo precedente, un ingresso digitale. Dunque, ha come scopo quello di rappresentare il segnale che arriva in ingresso con un certo numero di bit in uscita, determinati dal quantizzatore utilizzato nel modulatore.

Inizialmente è analizzata l'architettura scelta per realizzare il modulatore, spiegando anche il perché dei parametri utilizzati per realizzarla. Successivamente si è passati ad effettuare delle simulazioni del modulatore del quinto ordine con diversi parametri e due diversi quantizzatori.

## 4.1 MODELLO DEL MODULATORE

Nella letteratura sono state sviluppate molte diverse architetture, che variano tra di loro per diversi fattori come la massima risoluzione raggiungibile, la complessità del modulatore, la sensibilità agli effetti non ideali e le proprietà di stabilità. Questo ha portato a scegliere per questa tesi l'architettura mostrata in Figura 4.1 [16], che permette di migliorare la stabilità e di ridurre l'effetto del rumore, oltre a permettere di scegliere gli zeri della NTF.

Figura 4.1 - Architettura sigma-delta a più livelli.

Questa architettura presenta diversi componenti tra cui si trovano degli integratori, di numero pari all'ordine adottato, e dei sommatori. Questi ultimi si trovano a sommare l'uscita dell'integratore precedente con il segnale di uscita del modulatore, prima e dopo il passaggio attraverso il quantizzatore, scalato con dei coefficienti  $a_i$  e  $b_i$  con i=1, ..., n,

dove n è l'ordine del modulatore, che devono essere opportunamente scelti in modo da avere le funzioni STF e NTF desiderate, che avranno questa forma:

$$NTF = \frac{z(z-z_1)(z-z_1^*)(z-z_2)(z-z_2^*)...(z-z_n)(z-z_n^*)}{(z-p_1)(z-p_2)....(z-p_n)}$$

(4.1)

$$STF = \frac{1}{(z-p_1)(z-p_2)....(z-p_n)}$$

(4.2)

In particolare, in questa tesi si propone di adottare l'analisi proposta in [16] in cui si fa notare che i poli della STF e della NTF sono coincidenti. Inoltre, i poli vengono posti nella configurazione di Butterworth, scelta adottata sempre nello stesso articolo.

I poli della NTF sono quindi realizzati con un filtro passa alto di Butterworth di ordine n mentre la STF, creata con questi poli, diventa un filtro passa basso. Successivamente, riguardo la posizione degli zeri della NTF, si è visto come il posizionamento degli stessi influenzi il rapporto segnale-rumore del modulatore, spingendo a cercare delle posizioni ottime. Queste ultime sono state cercate e trovate e sono rappresentate nella Tabella 4.1 [15] per ordini fino all'ottavo. Utilizzando queste posizioni per gli zeri, si ottiene un miglioramento rispetto al posizionarli tutti in DC e il grafico in Figura 4.2 mostra il nuovo SNR massimo.

Si può quindi effettuare un confronto rispetto al precedente grafico in Figura 3.8 e notare il guadagno in termini di dB.

| dn | zero locations, normalized to $\omega_B$                              | SNR<br>improvement |

|----|-----------------------------------------------------------------------|--------------------|

| 1  | 0                                                                     | 0 dB               |

| 2  | $\pm \frac{1}{\sqrt{3}}$                                              | 3.5 dB             |

| 3  | $0, \pm \sqrt{\frac{3}{5}}$                                           | 8 dB               |

| 4  | $\pm\sqrt{\frac{3}{7}\pm\sqrt{(\frac{3}{7})^2-\frac{3}{35}}}$         | 13 dB              |

| 5  | $0, \pm \sqrt{\frac{5}{9} \pm \sqrt{(\frac{5}{9})^2 - \frac{5}{21}}}$ | 18 dB              |

| 6  | ±0.23862, ±0.66121, ±0.93247                                          | 23 dB              |

| 7  | $0, \pm 0.40585, \pm 0.74153, \pm 0.94911$                            | 28 dB              |

| 8  | ±0.18343, ±0.52553, ±0.79667, ±0.96029                                | 34 dB              |

Tabella 4.1 - Posizionamento ottimo degli zeri per aumentare l'SNR.

Figura 4.2 - SNR massimo utilizzando posizionamento ottimo per gli zeri.

Con questa architettura si presenta però, nel caso di ordini superiori al secondo, il problema della stabilità. Infatti, l'ingresso si deve trovare in un certo range di valori in modo da non far sovraccaricare il quantizzatore finale, altrimenti si arriva all'instabilità. Perciò qui viene utilizzata una scalatura dell'ingresso di un fattore  $\beta>0$ , mostrata in Figura 4.3 [16].

Figura 4.3 - Scalatura dell'ingresso u di un fattore  $\beta$ .

Il valore di  $\beta$  viene poi deciso basandosi sulle simulazioni in modo da garantire stabilità e far funzionare il quantizzatore nel modo desiderato.

Riguardo quest'ultimo, nelle simulazioni qui effettuate viene utilizzato prima un quantizzatore a tre livelli, quindi con una risoluzione di 1+½ bit, e successivamente a cinque livelli, con una risoluzione di 2+¼ bit, con caratteristica ingresso-uscita in Figura 4.4.

Figura 4.4 - Caratteristica del quantizzatore a cinque livelli.

In Figura 4.5 è poi mostrato il quantizzatore realizzato in Simulink utilizzando due blocchi, chiamati quantizzatore e saturazione. Il primo di essi svolge il ruolo di definire l'intervallo voluto di quantizzazione, mentre il secondo serve a definire i valori per cui far saturare il quantizzatore, permettendo quindi di fissare il numero dei livelli di quantizzazione.

Nel caso a tre livelli si fissa per il quantizzatore un intervallo di 1, con intervallo di funzionamento dato da [-1,1], al contrario, per i cinque livelli si utilizza lo stesso quantizzatore, ma con intervallo di [-2,2].

Figura 4.5 - Quantizzatore utilizzato per il modello in Simulink.

## 4.2 SIMULAZIONI DEL MODULATORE

Il progetto del modulatore è stato fatto tenendo conto del segnale adottato per l'ingresso, costituito da un segnale audio, ma per semplificare le simulazioni è stata utilizzata una sinusoide di ampiezza unitaria e frequenza di 10 kHz. Il segnale audio presenta tipicamente una frequenza di campionamento pari a 44.1 kHz, il che ci ha portati a scegliere inizialmente un valore di 25 come OSR, cioè oversampling ratio o fattore di interpolazione. In questo modo il modulatore si trova a lavorare con una frequenza di 1 MHz, la quale permette di ottenere un elevato rapporto segnale-rumore. Successivamente però abbiamo testato lo stesso circuito con una frequenza di campionamento doppia, pari quindi a 2 MHz, e si è notato un miglioramento nelle prestazioni, relativamente sia alla stabilità che al rapporto segnale-rumore, che ci ha portati a scegliere un OSR di 50 e quindi questa seconda opzione.

La scelta della frequenza di campionamento del sigma-delta e l'SNR desiderato ci hanno portato a scegliere un modulatore del quinto ordine, scelta sostenuta dalle simulazioni effettuate che hanno mostrato un'ottima efficienza.

I parametri per i coefficienti della retroazione a<sub>i</sub> e b<sub>i</sub> sono stati calcolati in modo da avere l'STF e l'NTF desiderate in accordo con quanto detto in [16], il che corrisponde ad un guadagno costante e ad una forte riduzione del rumore nella banda del segnale. Questo è ottenuto adottando le posizioni dei poli e zeri dette nel paragrafo precedente, che corrispondono per gli zeri alle posizioni suggerite nella Tabella 4.1 mentre per i poli a quelli di un filtro passa alto di Butterworth del quinto ordine con una frequenza di cutoff normalizzata pari a Kpoli/OSR, dove Kpoli è una costante che rappresenta il nostro unico

grado di libertà e al suo variare si modifica il comportamento di tutto il circuito e OSR corrisponde al fattore di oversampling.

Il quantizzatore è stato descritto nel paragrafo precedente e riproduce in uscita un segnale multilivello che viene poi filtrato. Il filtro qui utilizzato è un filtro passa basso digitale IIR dell'ottavo ordine (Figura 4.6) con una frequenza di cutoff di 22 kHz, valore che rappresenta la metà della frequenza di campionamento del segnale di ingresso. Questo permette di eliminare tutte le componenti fuori dalla banda del segnale e permette di avere in uscita una forma d'onda uguale a quella di partenza.

Figura 4.6 - Filtro digitale realizzato in Simulink.

Lo schema circuitale del modulatore sigma-delta, rappresentato nel Simulink con il nome di "sigmadelta\_modulator", è presentato in Figura 4.7, in cui è presente lo scaling dell'ingresso, effettuato utilizzando un blocco moltiplicatore pari a 1/k, dove k rappresenta il valore per cui viene scalato l'ingresso ed è stato ricavato sperimentalmente.

Figura 4.7 - Modello Simulink del modulatore sigma-delta.

# 4.2.1 RISULTATI SIMULAZIONI A 1 MHz

Inizialmente abbiamo svolto delle simulazioni del modulatore utilizzando una frequenza di campionamento pari a 1 MHz, ponendo quindi l'OSR uguale a 25, provando a variare alcuni parametri

Per prima cosa sono stati calcolati i valori dei coefficienti della retroazione utilizzando degli opportuni script MATLAB presentati nell'Appendice. Innanzitutto, è stato usato lo script "Costanti", contenente delle costanti che sono usate per definire le posizioni degli zeri e dei poli. In particolare, si tratta di "Kzeri", che indica la posizione degli zeri della NTF, e "Kpoli", usato per calcolare i poli di entrambe le funzioni di trasferimento; a questi si aggiunge inoltre la costante "k", utilizzata per effettuare lo scaling dell'ingresso.

Successivamente si utilizza lo script "NTF\_STF\_a\_b", il quale permette di calcolare in modo parametrico il numeratore e il denominatore delle funzioni di trasferimento in funzione dei parametri "a" e "b" seguendo il metodo descritto in [16].

Infine, si utilizza un nuovo script, chiamato "Totale", il quale calcola i valori numerici dei coefficienti della retroazione attraverso due funzioni, sempre definite in MATLAB. La prima di esse è rappresentata da "Num\_Den" che svolge il calcolo delle funzioni di trasferimento, quindi dei valori del numeratore e denominatore delle due funzioni,

prendendo in ingresso "Kzeri" e "Kpoli", già definiti in precedenza, e "OSR", cioè il fattore di oversampling. In questo modo si ottengono la STF e la NTF con le posizioni degli zeri e dei poli già indicate nel paragrafo 4.2. Dopo aver usato questa funzione, lo script "Totale" ne utilizza anche un'altra, chiamata "Coefficienti\_Sdmod" che risolve il sistema lineare per calcolare i coefficienti del modulatore.

Una volta calcolato questo, sono state fatte delle simulazioni per diversi valori di Kpoli, attraverso le quali abbiamo visto per quali valori presenta un comportamento stabile o instabile e si è calcolato il rapporto segnale rumore attraverso lo script "Risultati", nello specifico utilizzando la funzione "snr\_function", la quale prende in ingresso il segnale e il rumore. In particolare, si è notato che nel caso del quantizzatore a cinque livelli il modulatore risulta stabile con un ingresso unitario solo per il valore di Kpoli uguale a 4, presentando un SNR pari a 85.2 dB. Rappresenta quindi il valore scelto per il modulatore e in questo modo l'uscita risulta uguale all'ingresso, come mostrato in Figura 4.8, in cui nella parte superiore si trova l'uscita e in quella inferiore l'ingresso.

Figura 4.8 - Uscita (sopra) e ingresso (sotto) del sigma delta con quantizzatore a cinque livelli.

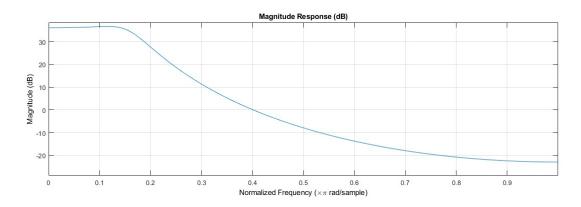

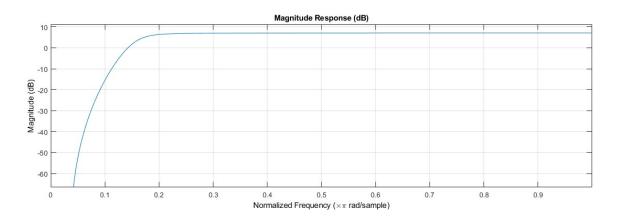

Questo modulatore con il valore di Kpoli uguale a 4 presenta anche delle funzioni STF e NTF accettabili, dal momento che la STF, in Figura 4.9, ha andamento costante nella banda di interesse con un guadagno che vale 36 dB, corrispondente in scala lineare a 63. Questo valore di 63 è anche quello scelto per il coefficiente di scaling "k", necessario per avere l'uscita stabile e unitaria. La NTF invece presenta un comportamento passa alto,

con una forte attenuazione nella banda. È mostrata in Figura 4.10 e ha un andamento che rispetta le aspettative.

Figura 4.9 - Grafico della funzione di trasferimento del segnale o STF.

Figura 4.10 - Grafico della funzione di trasferimento del rumore o NTF.

Nel caso del quantizzatore a tre livelli nasce il problema della stabilità anche per Kpoli uguale a 4, infatti diventa instabile anche con questo valore nel caso di ingresso ad ampiezza unitaria. La ragione è data dal fatto che, con un ingresso troppo elevato, il quantizzatore viene sovraccaricato. Per ottenere la stabilità è necessario quindi, sempre con Kpoli uguale a 4, ridurre l'ampiezza della sinusoide fino al valore di 0.3, con il quale si ottiene un SNR di 74.9 dB. Questo risulta minore rispetto al precedente a cinque livelli poiché diminuisce la risoluzione, che passa da 2+1/4 bit dei cinque livelli ai 1+1/2 bit dei tre livelli.

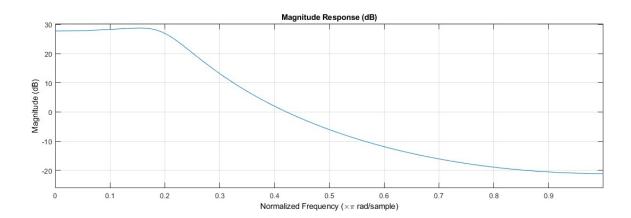

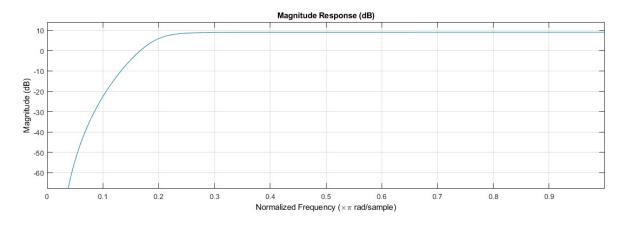

# 4.2.2 RISULTATI SIMULAZIONI A 2 MHz

Dopo aver testato il modulatore con una frequenza di campionamento di 1 MHz, si è provati a raddoppiare la frequenza, ponendo quindi un OSR pari a 50, in modo da vedere se miglioravano le prestazioni e si è notato un effettivo cambiamento.

Inizialmente sono calcolati i coefficienti del modulatore con lo stesso metodo presentato nel paragrafo 4.2.1. Infatti, inizialmente viene usato lo script "Costanti2M", contenente le stesse costanti di "Costanti", con opportune modifiche ai valori, a cui si fa seguire lo script "NTF STF a b", già utilizzato per la simulazione a 1 MHz.

Infine, attraverso lo script "Totale2M", che riprende le stesse funzioni precedentemente usate per "Totale", cioè "Num\_Den" e "Coefficienti\_Sdmod", si calcolano i valori numerici dei coefficienti della retroazione.

Dopo aver definito tutti i parametri del modulatore, sono state fatte prove per diversi valori di Kpoli, che hanno evidenziato miglioramenti in termini di rapporto segnale-rumore di diversi dB, oltre ad una maggiore flessibilità con il segnale di ingresso.

Il calcolo delle prestazioni è stato effettuato utilizzando lo script "Risultati2M", con cui attraverso la funzione "snr\_function" si calcola il rapporto segnale rumore. In particolare, utilizzando sempre lo stesso quantizzatore a cinque livelli esposto alla fine del paragrafo 4.1, sono stati trovati dei risultati per diversi valori di Kpoli, esposti nella Tabella 4.2, che evidenziano ora un picco massimo di SNR ottenibile pari a 126 dB.

| kpoli | SNR       |

|-------|-----------|

| 2     | 60 dB     |

| 4     | 91.7 dB   |

| 7     | 111.7 dB  |

| 9     | 122.6 dB  |

| 10    | 126 dB    |

| 11    | instabile |

Tabella 4.2 - Tabella degli SNR ottenuti nelle simulazioni a 2 MHz.